Diode Logic

Consider the following diode network with two resistors and , a light bulb, and three toggle switches S1, S2, and S3:

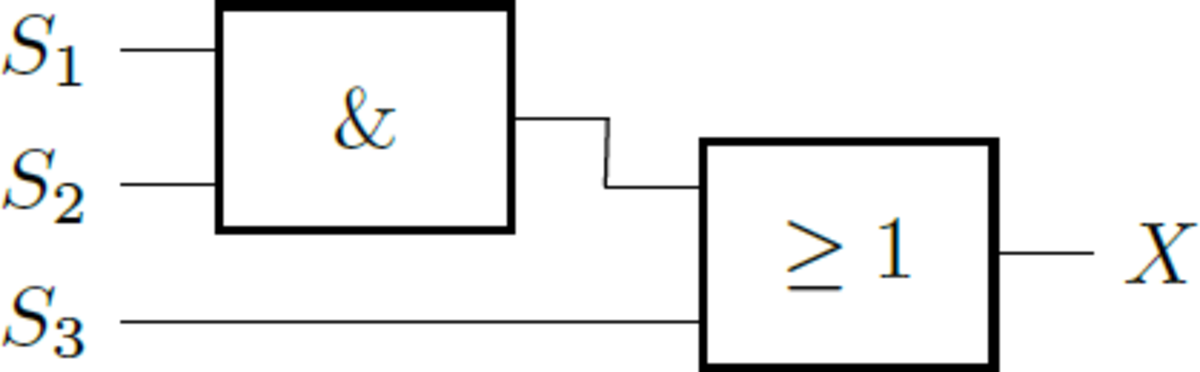

Which switch positions ensure that the light bulb is lit? Consider the circuit as a logical gate with the voltage (high level) as TRUE and (low level) as FALSE. The switches are the inputs of the logic gate, while the bulb serves as an output. Which logical expression represents the whole circuit?

In the answer options, we use the following abbreviations:

Assumptions: For the resistors, applies so that in the off position of all switches, the electrical voltage drops practically only at the resistance , so that the output is at a low level and the lamp is not lit. Take the diodes as ideal rectifiers, which have no resistance in the forward direction and completely block the current flow in the reverse direction.

This section requires Javascript.

You are seeing this because something didn't load right. We suggest you, (a) try

refreshing the page, (b) enabling javascript if it is disabled on your browser and,

finally, (c)

loading the

non-javascript version of this page

. We're sorry about the hassle.

We first consider the first diode pair. If one of the two switches S1 and S2 is in the off position, the corresponding diode is switched in the forward direction, so that a current flows through the resistor. Since the diode has no resistance in this position, the entire voltage drops at the resistor, so that the output is at zero potential. However, if both switches S1 and S2 are on, all nodes are at high level, so that also exists at the output of the potential U = + U 0 . The diode pair therefore acts as an AND gate with respect to the switches S1 and S2, so that the output has high level if and only if both switches are on.

The second pair of diodes is reversed poled, so that the current flows if one of the two inputs is at high level. In this case, the entire voltage drops again at the resistor, so that the output has the potential U = + U 0 . If both inputs are at low level ( U = 0 ), this applies also to the output. This circuit is thus an OR gate.

Thus, the entire circuit is represented by the expression

L = ( S 1 AND S 2 ) OR S 3